文/吳旻蓁

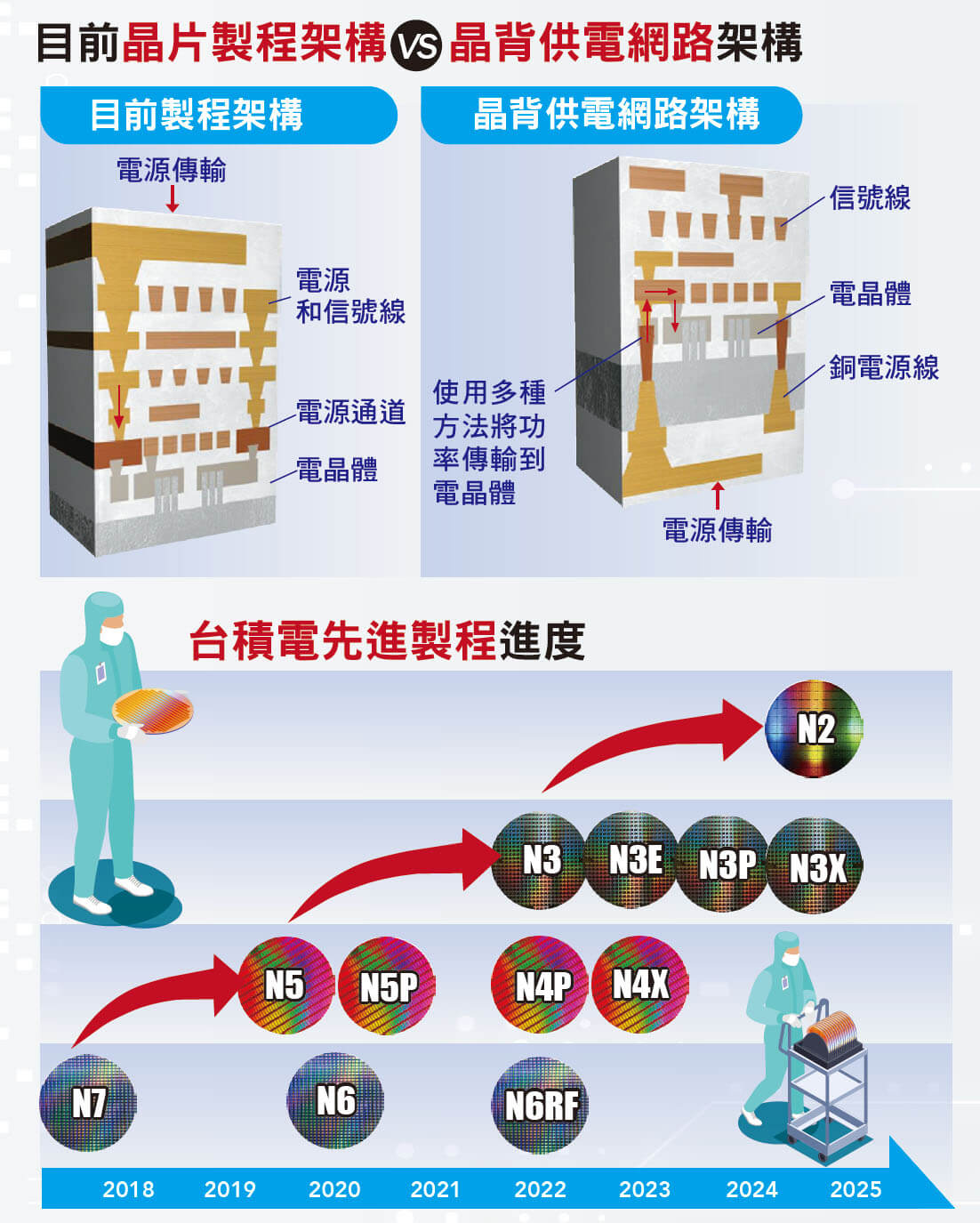

晶圓代工龍頭廠台積電(2330)在十九日法說會上除了提及三奈米製程進度外,總裁魏哲家也透露觀察到二奈米在高速運算和智慧手機相關應用方面獲得客戶興趣和參與,與三奈米在同一階段時不相上下、甚至更高。而台積電預計二奈米將如期於二五年量產,且表示二奈米推出時,將是業界最先進的半導體技術;而適用於HP C的二奈米「背面電軌」(backside power rail)解決方案則預定二五年下半年推出、二六年量產。

▲台積電、英特爾和三星都宣布計畫在二奈米節點附近以某種形式實施晶背供電技術 組合照片

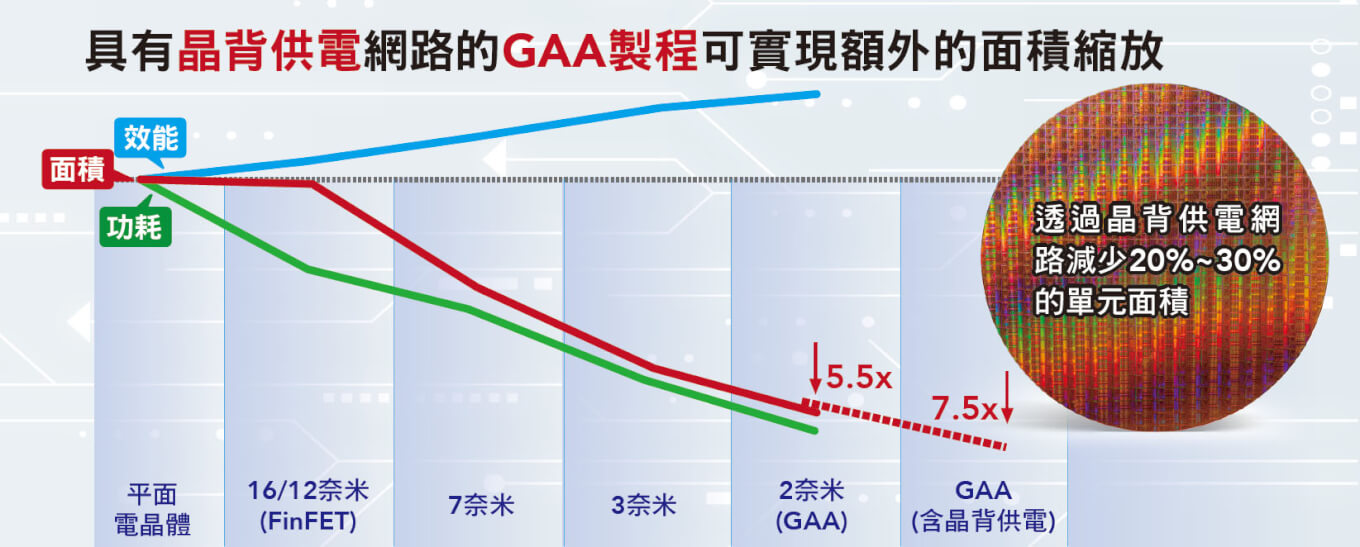

事實上,自二二年以來,台積電就多次發表二奈米晶片製程的研發進度;在今年的技術研討會上,台積電也表示N2P製程技術將通過晶背供電網路(BackSidePower Delivery Network; BSPDN)減少IR壓降(IR Drop)和改善信號,將性能提高十到十二%,並將邏輯面積減少十到十五%。

當前隨著電晶體逼近單奈米尺度,甚至比新冠病毒顆粒(約一二○奈米)還小,如何製作出更迷你、效能更高、能夠短時間量產的下一代元件,是半導體產業近年來一大棘手問題。也因此,晶片製造競爭持續白熱化,台積電、英特爾(Intel)、三星(Samsung)等晶片製造巨頭都在爭相展示三奈米、二奈米等先進工藝的技術突破,包括GAA(閘極全環電晶體)、High-NA(高數值孔徑)、先進封裝等一系列的創新技術,都是為了替摩爾定律續命。

而與EUV光刻機類似,晶背供電技術被視為繼續開發更精細工藝節點的關鍵技術,預期將成為晶片廠又一個新的競爭戰場。晶背供電技術的出現,為晶片製造帶來了一些全新的製程步驟。過去長久以來,晶片製造都是利用後段製程(BEOL),在矽晶圓的正面布線,透過這些低電組的導線來供應電力給晶片;也因為如此,晶片內的供電網路與訊號網路(即晶片內的訊號線)必須共用相同的元件空間。

但在製程節點持續推進之下,電晶體越來越小,密度越來越高,堆疊層數也越來越多,為了將電力從封裝傳輸至晶片中的晶體管,電子必須經由金屬導線和通孔,穿過十到二○層堆疊才能為下方電晶體提供電源和數據訊號。然而,越接近晶體管,線寬和通孔就越窄,電阻值也因而上升,使得電子在向下傳輸的過程中,會出現IR壓降現象,導致電力損失產生。

除了電力損失,供電線路占用空間也是問題。晶片內的電源線路在布線複雜的後段製程上,往往占至少二○%的繞線資源,如何解決訊號網路跟供電網路之間的資源排擠問題,使元件進一步微縮,變成晶片設計者所面臨的主要挑戰之一。此外,電源線和接地線在標準單元設計上占了很大空間,使得組件很難進一步微縮。就系統設計而言,因為功率密度和IR壓降急遽增加,從穩壓器到晶體管的功率損失就很難控制在十%以下。對此,專家指出,如果不對晶片的電子進出方式進行大改變,無論製造多小的晶體管都無濟於事,也因此,業界開始研究將供電網路轉移到晶片背面的可能性。

所謂晶背供電網路,顧名思義,就是把整個配電網路都移到晶圓背面,能對標準單元進行直接供電,不僅導線更寬、電阻更低,而且電子還不需要層層穿越後段製程的元件堆疊,如此一來,緩解了IR壓降的問題,大幅改善晶片性能,同時,也因分離邏輯IC的電源供應網路與訊號線,進而減緩了後段製程布線壅塞的問題,而且還能透過設計技術協同優化(DTCO),在標準單元實現更有效率的導線設計,進而協助縮小邏輯標準單元的尺寸,還有望實現像是邏輯與記憶體堆疊等3D系統單晶片的設計。此外,也因為將電源分配到背面,使下面的金屬層將形成一個更寬松的間距,這意味著可以減少E UV的光刻次數,進而降低成本。

自二○一九年,比利時微電子研究中心(imec)首次提出晶背供電技術的概念之後,不同的製程方案也隨之出現,應用材料指出,根據目前市面上已公布的三種晶背供電網路實現方式來看,包括第一種為埋入式電源軌(BPR),就是邏輯單元保留電源軌,並且晶背供電網路通過奈米矽穿孔(nTSV) 連接到電源軌。

第二種方式是邏輯單元中沒有電源軌,而是依靠nTSV直接將電源從晶背供電網路傳輸到單元或電晶體接點;這種方法更複雜,但因避免了電源軌所需的接線,因此提高了功率效率並增加了單元面積縮放,而這也是英特爾著力的方向。至於第三種是來自晶背供電網路的電源將直接連接到每個電晶體的源極(source)和汲極(drain),這也是三種方式中最複雜的。

儘管目前晶背供電技術尚未成熟,但在技術優勢的吸引下,台積電、英特爾、三星等晶片大廠都相當積極在其邏輯晶片的開發藍圖中導入此技術。尤其,晶背供電可以說是英特爾欲在先進工藝奪回領先地位的一大重要布局。二一年重返晶圓代工市場的英特爾,同年就公告了兩項創新技術,除了採用GAA技術的RibbonFET電晶體架構外,另一個就是晶背供電技術,並將其命名為「PowerVia」。

英特爾目前為業界第一家在類產品(Product-like)的測試晶片上實作晶背供電的公司,且在六月的VLSI研討會上,其展示了PowerVia過程,並公布已經有良好性能的測試結果。據測試結果顯示,晶片大部分區域的標準單元利用率都超過九○%,平台電壓降低三○%,並實現六%頻率提升,同時單元密度也大幅增加,並有望降低成本。此外,PowerVia測試晶片也展示良好的散熱特性,符合邏輯微縮預期將實現的更高功率密度。對此,英特爾預計將在二四年量產的二○A(二奈米)以及之後的十八A(一.八奈米)製程節點中,為晶圓代工服務的客戶提供此一技術選項。 而據研究機構指出,相對於英特爾,台積電首次嘗試選擇的實現方式為複雜度較低的埋入式電源軌,因為可以在現有的工具上完成,因此成功率也比較高。不過,關於如何實施晶背供電網路技術,目前台積電尚未有過多透露,但其3D IC封裝技術SoIC,是實現晶背供電的重要前提。

至於三星,先前也公布研究數據,表示與傳統前端供電網路相比,晶背供電網路成功將耗用晶圓面積減少十四.八%,晶片能擁有更多空間,可增加更多晶體管,提高整體性能;布線長度減少也九.二%,有助降低電阻、使更多電流通過,進而降低功耗,改善功率傳輸狀況。三星則計畫在二七年將晶背供電技術應用於一.四奈米製程上。 閱讀完整內容